# **TDE3 – Logique combinatoire – Portes logiques**

| Capacités exigibles                                                                                                        | ChE3 | TDE3 | TP5 |

|----------------------------------------------------------------------------------------------------------------------------|------|------|-----|

| Interrupteurs commandés par une tension.                                                                                   |      |      |     |

| Porte logique NOT.                                                                                                         |      |      |     |

| Portes logiques AND, OR, NAND, NOR à deux ou plusieurs entrées.                                                            | _    |      | _   |

| Porte logique XOR.                                                                                                         | •    | •    | •   |

| Déterminer la table de vérité d'une association d'interrupteurs commandés par une tension.                                 |      |      |     |

| Identifier par sa table de vérité la porte logique réalisée par une association d'interrupteurs commandés par une tension. |      |      |     |

### 0 Exercices classiques vus en cours :

B: Identification des portes logiques correspondant à un circuit à interrupteurs commandés

**C.1**: Justification d'égalités dans l'algèbre de Boole

C.2 : Justification de l'expression de l'opération XOR en fonction des opérations NOT et OR

C.3: Justification des lois de de Morgan

C.3: Justification de l'obtention des opérateurs NOT, AND et OR via des associations de portes NAND

## 1 Algèbre de Boole

Montrer que :

| Règles élémentai | ires | : |

|------------------|------|---|

|------------------|------|---|

1)

$$a \cdot a = a \ et \ a + a = a$$

2)

$$(a + b) + c = a + (b + c)$$

3)

$$a \cdot (b+c) = a \cdot b + a \cdot c$$

## Simplifications:

$$4) \quad a + a \cdot b = a$$

5)

$$a + \overline{a} \cdot b = a + b$$

6)

$$a \cdot (\overline{a} + b) = a \cdot b$$

## Propriétés de l'opérateur NOT :

7)

$$a + \overline{a} = 1$$

et  $a \cdot \overline{a} = 0$

8)

$$\overline{a+b} \neq \overline{a} + \overline{b}$$

9)

$$\overline{a \cdot b} \neq \overline{a} \cdot \overline{b}$$

10)

$$\overline{a \cdot (b+c)} \neq \overline{a} \cdot (\overline{b} + \overline{c})$$

# 2 / Groupe complet de la porte NOR

En utilisant une loi de de Morgan, proposez, à l'aide uniquement de portes NOR, un circuit logique permettant de réaliser les opérations NOT, AND et OR.

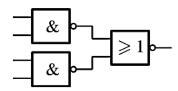

#### 3 Réalisation d'une porte AND à 4 entrées

**○** Montrer que cette association de portes logiques correspond à une porte AND à 4 entrées i.e. que la sortie vaut 1 uniquement si toutes les entrées valent 1.

#### 4 Porte XOR

- 1. On note a et Y les deux entrées d'une porte XOR. L'entrée Y est nommée commande. Exprimer la sortie s en fonction de l'entrée a lorsque Y=0. Même question lorsque Y=1.

- 2. Détecteur d'imparité :

- (a) On réalise une porte XOR sur trois entrées  $a \oplus b \oplus c$ . Montrez que

$$a\oplus b\oplus c=c\cdot b\cdot a+c\cdot \bar{b}\cdot \bar{a}+\bar{c}\cdot \bar{b}\cdot a+\bar{c}\cdot b\cdot \bar{a}\ .$$

- (b) En déduire que cette sortie vaut 1 uniquement si le groupe (a, b, c) contient un nombre impair de 1.

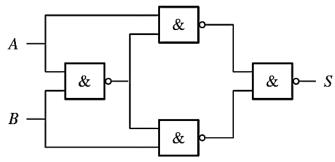

- 3. Réalisations

- (a) Montrer que le circuit logique ci-dessus réalise une porte XOR.

- On rappelle que l'opération XOR est donné par  $a \oplus b = \overline{b} \cdot a + b \cdot \overline{a}$ .

- (b) Proposer un circuit logique équivalent à la porte XOR constitué uniquement de portes NOT, AND et OR.

- (c) À partir de la question précédente, proposez un circuit logique permettant de réaliser l'opération XNOR.

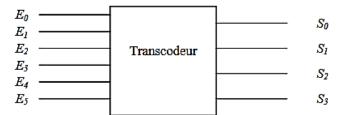

## 5 Exemple de transcodeur : afficheur hexadécimal sept segments

Le transcodeur sert à passer d'un code à un autre. On calcule chaque sortie  $S_j$  en fonction des combinaisons des entrées  $E_i$ .

On souhaite afficher sur un afficheur 7 segments (diodes électroluminescentes LED) le chiffre ou la lettre correspondant à un nombre binaire :

En entrée, on a un nombre binaire de 4 bits qui correspond aux valeurs de 0 à F en hexadécimal. En sortie, on cherche le pilotage des sept segments de l'afficheur soit 7 sorties.

Chaque segment est relié à une LED. Dans cet exercice, nous avons choisi l'état allumé égal à 1. Par convention, les segments sont numérotés dans l'ordre alphabétique. La numérotation se fait en spirale, en partant du haut, conformément à la figure ci-contre.

Les données d'entrées sont enregistrées sur 4 bits notés xyzt. Le tableau ci-dessous rappelle les valeurs à prendre ainsi que le caractère à afficher sur l'afficheur.

| Héxadécimal | 0    | 1    | 2    | 3    | 4            | 5         | 6         | 7         |

|-------------|------|------|------|------|--------------|-----------|-----------|-----------|

| Binaire     | 0000 | 0001 | 0010 | 0011 | 0100         | 0101      | 0110      | 0111      |

| Affichage   | 0    | 1    | 2    | 3    | 4            | 5         | 6         | 7         |

|             |      |      |      |      |              |           |           |           |

| Héxadécimal | 0    | _    |      |      |              |           |           |           |

| nexadecimai | 8    | 9    | A    | В    | $^{\circ}$ C | D         | $_{ m E}$ | F         |

| Binaire     | 1000 | 1001 | 1010 | 1011 | 1100         | D<br>1101 | E<br>1110 | F<br>1111 |

- 1. Remplir la table de vérité donnant la sortie abcdefg en fonction du mot binaire d'entrée xyzt.

- 2. Proposer une formule booléenne pour a permettant de répondre à cette table de vérité.

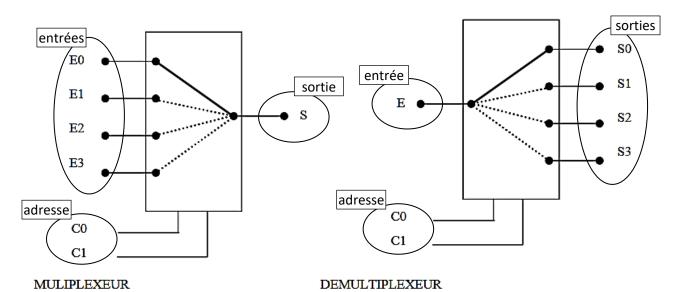

## 6 Multiplexeur et démultiplexeur

Un multiplexeur est un circuit d'aiguillage commandé : on retrouve en sortie une des entrées choisie grâce à la commande d'adresse. Le démultiplexeur effectue l'opération inverse.

### Schémas de principe du Multiplexeur et du démultiplexeur :

On étudie un multiplexeur à deux entrées, notées  $e_0$  et  $e_1$ , et un bit d'adresse a. La sortie vaut  $e_0$  si a=0 et  $e_1$  dans le cas contraire.

- 1. Écrire la table de vérité du multiplexeur.

- 2. Montrer que la sortie est équivalente à  $\overline{a} \cdot e_0 + a \cdot e_1$

- 3. En déduire le schéma logique correspondant.

On étudie un démultiplexeur à deux sorties, notées  $s_0$  et  $s_1$ , et un bit d'adresse  $s_0$ . La valeur du bit d'entrée  $s_0$  et transmise à la sortie  $s_i$  selon la valeur du bit d'adresse  $s_0$  et  $s_0$  et  $s_1$  e si  $s_2$  e si  $s_3$  e sortie qui ne correspond pas au bit d'adresse.

- 4. Écrire la table de vérité du démultiplexeur.

- 5. Proposer un schéma logique correspondant.