# Chapitre E4. Logique séquentielle

En logique séquentielle, on distingue les entrées et sorties principales, celles qui sont en quelque sorte visibles de l'extérieur par l'utilisateur, et les entrées et sorties secondaires, qu'on nommera variables internes au circuit et qui introduisent l'aspect temporel.

Les variables internes sont en effet rebouclées sur les entrées principales à travers un bloc introduisant un retard.

#### INTRO:

Dans le ChE3, on s'est intéressé à la **logique combinatoire** dans laquelle <u>l'état de sortie ne dépend que de l'état des variables d'entrée</u>.

On étudie ici des systèmes <u>bouclés</u>: une sortie est connectée à une entrée du système, on parle de <u>RETROACTION</u>. Pour analyser leur fonctionnement, il faut prendre en compte la dimension temporelle: l'évolution des tensions auxquelles correspondent les signaux logiques en fonction du temps. Dans ce chapitre, on tiendra donc compte du temps de commutation ou de la tension seuil  $V_s$  des portes logiques.

On parle alors de <u>LOGIQUE SEQUENTIELLE</u> où <u>l'état de sortie dépend</u> non seulement de l'état présent des variables d'entrée <u>mais aussi de l'état précédent de la sortie</u>. Ainsi à une combinaison d'états des variables d'entrée peuvent correspondre plusieurs états possibles de la sortie. C'est ce qui fait la richesse des comportements de ces circuits grâce auxquels de nombreuses fonctionnalités peuvent être réalisées (mémoire par exemple).

Les systèmes séquentiels (oscillateur, convertisseur fréquence-tension et bascule RS) étudiés dans ce chapitre sont constitués de portes logiques et éventuellement de dipôles passifs (résistance, condensateur).

<u>Buts de ce chapitre</u>: Etudier la stabilité d'un système; Décrire le fonctionnement de systèmes séquentiels astable, monostable et bistable (bascule RS); Construire et/ou exploiter des chronogrammes.

#### Préreguis:

1e année : Signaux et composants électriques ; Régimes transitoires.

MPI: E3 Logique combinatoire.

#### Plan du chapitre:

| A) Description d'un système sequentiel                                                        | 2 |

|-----------------------------------------------------------------------------------------------|---|

| 1) Variables logiques                                                                         | 2 |

| 2) Chronogramme                                                                               | 2 |

| 3) Etat stable – Circuits astable, monostable, bistable                                       | 3 |

| B) Exemples de circuits astables (Cours-TD)                                                   | 4 |

| 1) Oscillateur à 3 portes NOT                                                                 | 4 |

| 2) Oscillateur à 2 portes, un condensateur et une résistance (circuit proche dans CCINP 2024) | 4 |

| C) Ex de circuit monostable : convertisseur fréquence-tension (Cours-TD)                      | 5 |

| D) Ex de circuit bistable : bascule RS – mémoire Set-Reset                                    | 7 |

| 1) Comportement d'une bascule RS – Effet mémoire                                              | 7 |

| 2) Réalisations pratiques (Cours-TD)                                                          | 8 |

# A) Description d'un système séquentiel

## 1) Variables logiques

- ◆ Dans un circuit séquentiel, on va distinguer trois types de variables logiques :

- **Entrées** principales : entrées  $\{E_i\}$  connectées à l'extérieur

- **Sorties** principales : sorties  $\{S_i\}$  récupérées par l'extérieur (tout circuit a au moins une sortie principale)

- Variables internes  $\{X_i\}$  pour toutes les entrées / sorties des portes logiques autres que les entrées / sorties principales.

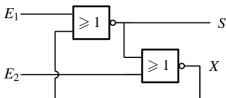

➡ Lister les entrées principales, les sorties principales et les variables internes du circuit ci-contre.

## ♦ Rappels du ChE3:

Pour une variable logique Y, on note  $u_Y$  la tension qui lui correspond.

$$u_Y < V_s \Leftrightarrow Y = 0 \ et \ u_Y > V_s \Leftrightarrow Y = 1$$

,  $V_s$  étant la tension seuil.

Dans tout ce chapitre, on supposera que  $V_s=rac{v_{dd}}{2}.$

La valeur de  $V_{dd}$  dépend du montage et de la technologie, on peut avoir  $V_{dd}=5\ V$  par exemple.

<u>NB</u>: Pour une variable logique Y qui est la <u>sortie d'une porte logique</u>, seules deux valeurs de tension sont accessibles: on a  $Y = 0 \iff u_Y = 0 \iff u_Y = 1 \iff u_Y = V_{dd}$ .

## 2) Chronogramme

Pour un jeu de variables d'entrée  $\{E_i\}$  fixé, l'état d'un circuit séquentiel est décrit par les valeurs des variables internes  $\{X_i\}$  et des sorties  $\{S_i\}$ . Cet état dépend a priori du temps même quand les entrées gardent des valeurs constantes dans le temps.

Un **CHRONOGRAMME** est un graphique représentant l'évolution des variables logiques  $\{E_i\}$ ,  $\{S_i\}$  et  $\{X_i\}$  au cours du temps.

# a) Exemple d'un circuit sans rétroaction :

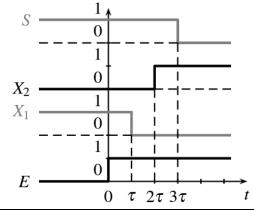

Supposons que pour t < 0, les variables soient dans les états suivants E = 0,  $X_1 = 1$ ,  $X_2 = 0$  et S = 1. A t = 0, E bascule au niveau logique 1. Pour établir le chronogramme des signaux logiques  $X_1$ ,  $X_2$  et E pour E pour E pour utilise la table de vérité de la porte NOT et on tient compte de son temps de commutation, noté E: il s'agit du temps de propagation des éventuels changements des entrées vers les sorties, de l'ordre de la dizaine de E0 pour les composants utilisés en TP.

## b) Exemple d'un circuit avec rétroaction :

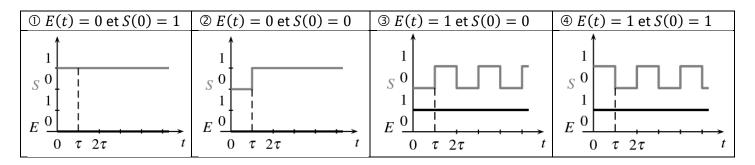

On trace les chronogrammes pour différentes valeurs du signal d'entrée E (maintenu à une valeur fixe) et différentes valeurs initiales du signal de sortie S. Pour cela, on utilise la table de vérité de la porte NAND et on tient compte de son temps de commutation, noté  $\tau$ .

- ♦ Lorsque l'entrée E = 0 (cas ① et ②), on constate que

- L'état S = 1 se maintient dans le temps

- L'état S = 0 ne perdure pas : il évolue vers l'état S = 1.

Conclusion : Pour la situation E = 0, S = 1 est dit **état stable** et S = 0 est dit **état instable**.

♦ Lorsque l'entrée E=1 (cas ③ et ④), on constate qu'aucun des deux états S=0 et S=1 n'est stable et que chacun évolue vers l'autre, donnant naissance à des **oscillations** de période  $2\tau$ .

Rappel :  $\tau \approx 10 \, ns$  pour les composants utilisés en TP.

# 3) Etat stable - Circuits astable, monostable, bistable

Pour un jeu de signaux d'entrée  $\{E_i\}$  constants donné, un <u>ETAT STABLE</u> d'un circuit est un état dans lequel les signaux de sortie  $\{S_i\}$  et les variables internes  $\{X_i\}$  ne varient pas dans le temps.

Les états stables sont tels que **toutes les relations logiques imposées par les portes sont satisfaites**, on parle d'état consistant. A l'inverse, les états inconsistants sont instables.

Ex : Pour le circuit du § A.2.b, la relation logique imposée par la porte est  $S = \overline{E \cdot S}$ .

La sortie de la porte reçoit une valeur  $S_-$  en entrée et la transforme en  $S_+ = \overline{E \cdot S_-}$  au bout d'un temps  $\tau$ . Si  $S_+ = S_-$  l'état est stable.

L'état  $\{E = 0, S = 1\}$  est stable.

En revanche, les états  $\{E=0,S=0\}$ ,  $\{E=1,S=0\}$  et  $\{E=1,S=1\}$  sont inconsistants et donc instables.

A un jeu de données d'entrée peuvent correspondre 0, 1 ou plusieurs états stables.

Si pour un jeu de données d'entrée, le circuit :

- n'a aucun état stable alors on qualifie le circuit d'ASTABLE;

- a exactement un état stable alors on qualifie le circuit de MONOSTABLE ;

- a exactement deux états stables alors on qualifie le circuit de BISTABLE.

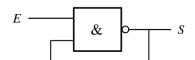

#### Ex:

Le circuit du § A.2.b est monostable pour E=0 et astable pour E=1.

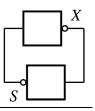

Le circuit ci-contre, nommé « point mémoire », est bistable : les états  $\{X=0,S=1\}$  et  $\{X=1,S=0\}$  sont stables. Ainsi construit, ce circuit n'est pas opérationnel, il faut lui ajouter des entrées de commande, cf § D (bascule RS).

# B) Exemples de circuits astables (Cours-TD)

Un circuit astable permet d'obtenir des oscillations i.e. de générer un signal périodique.

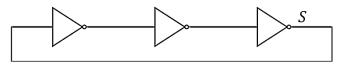

## 1) Oscillateur à 3 portes NOT

lacktriangle Vérifier que ce circuit est <u>astable</u> puis établir son chronogramme en tenant compte du temps de commutation des portes logiques et en considérant qu'à t=0, S bascule de 1 à 0.

Ce circuit et celui du § A.2.b sont des exemples élémentaires. Leur inconvénient est qu'on ne maîtrise pas la période d'oscillations car elle dépend du temps de commutation des portes logiques. Pour pallier ce défaut, on construit des circuits mettant en jeu des portes logiques et des circuits analogiques, cf ci-après.

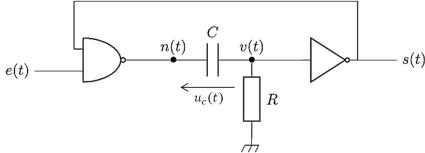

## 2) Oscillateur à 2 portes, un condensateur et une résistance (circuit proche dans CCINP 2024)

#### Hypothèses:

- les courants d'entrée des portes logiques sont supposés nuls (portes logiques idéales)

- le temps de commutation  $\tau$  des portes logiques est négligé car il est très inférieur au temps caractéristique du circuit  $\tau_c=RC$  ( $\tau\approx 10~ns$  et en TP,  $R\approx 100~k\Omega$  et  $C\approx 10~nF$ ).

#### ⇒ Etude du circuit :

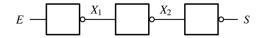

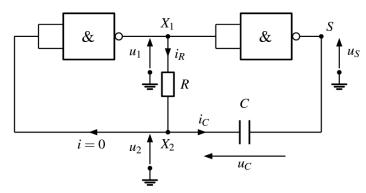

Pour ce circuit, on identifie une sortie principale S et deux variables internes  $X_1$  et  $X_2$ .

$X_1$  et S sont des sorties de portes logiques ainsi  $X_1 = 0 \Leftrightarrow u_1 = 0$  et  $X_1 = 1 \Leftrightarrow u_1 = V_{dd}$  et idem pour S.

- a) Quelle est la fonction d'une porte NAND lorsque ses deux entrées sont reliées entre elles ?

- b) Etats stables: Montrer par l'absurde que ce circuit n'a aucun état stable: ce circuit est astable.

- c) Equation différentielle (ED) : Montrer que  $u_c(t)$  vérifie l'ED :  $\frac{du_c}{dt} + \frac{u_c}{\tau_c} = \frac{u_1(t) u_s(t)}{\tau_c}$  avec  $\overline{\tau_c} = RC$ .

- d) Fonctionnement du circuit :

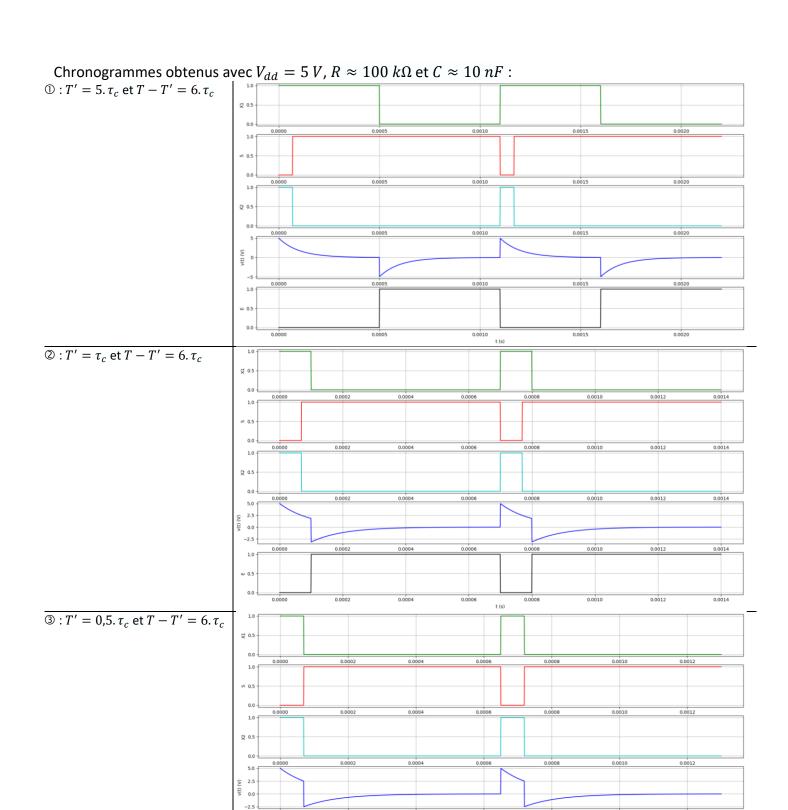

- i) On considère une 1<sup>e</sup> phase qui débute à l'instant t=0 tel que  $X_2$  bascule de 0 à 1. Autrement dit, à t=0, la tension  $u_2$  atteint la valeur seuil  $\frac{V_{dd}}{2}$  dans le sens croissant  $\Longrightarrow u_2(0^-) = \frac{V_{dd}}{2}$ . Tant que  $X_2=1$ , que valent  $u_1(t)$  et  $u_s(t)$ ? Résoudre l'équation différentielle vérifiée par  $u_c(t)$ . En déduire que  $u_2(t)=3\frac{V_{dd}}{2}e^{-t/\tau_c}$  et que cette 1<sup>e</sup> phase prend fin à  $t_1=\tau_c.\ln 3$ .

- ii) On considère une 2<sup>e</sup> phase qui débute à l'instant  $t=t_1$  tel que  $X_2$  bascule de 1 à 0. Tant que  $X_2=0$ , que valent  $u_1(t)$  et  $u_s(t)$ ? Résoudre l'équation différentielle vérifiée par  $u_c(t)$ . En déduire que  $u_2(t')=-3\frac{v_{dd}}{2}e^{-t'/\tau_c}+V_{dd}$  avec  $t'=t-t_1$  et que cette 2<sup>e</sup> phase prend fin à  $t_2'=\tau_c.\ln 3$ .

- iii) En déduire le chronogramme de ce système.

**BILAN**: Le signal  $u_s(t)$  est un **signal créneau** oscillant entre 0 et  $V_{dd}$  avec une **période**  $T=2RC\ln 3$ .

# C) Ex de circuit monostable : convertisseur fréquence-tension (Cours-TD)

Le principe de ce montage est d'exploiter un <u>état instable de durée déterminée</u> pour générer un signal de sortie s(t) dont la valeur moyenne est une fonction affine de la fréquence  $f=\frac{1}{T}$  du signal d'entrée e(t). On obtient ainsi un convertisseur fréquence-tension.

### Hypothèses: idem § B.2

- les courants d'entrée des portes logiques sont supposés nuls (portes logiques idéales)

- le temps de commutation  $\tau$  des portes logiques est négligé car  $\tau \ll \tau_c = RC$ .

### ⇒ Etude du circuit :

Pour ce circuit, on identifie une entrée principale E, une sortie principale S et deux variables internes  $X_1$  relative au potentiel n(t) et  $X_2$  relative au potentiel v(t).

$X_1$  et S sont des sorties de portes logiques ainsi  $X_1=0 \Leftrightarrow n=0$  et  $X_1=1 \Leftrightarrow n=V_{dd}$  et idem pour S. La **tension d'entrée** e(t) est une tension **créneau** de période T qui vaut  $\mathbf{0}$  pour  $\mathbf{t} \in ]\mathbf{0}, T'[$  et qui vaut  $\mathbf{V}_{dd}$  pour  $\mathbf{t} \in ]T', T[$ .

- a) Etats stables: Montrer que, pour E=0, l'état  $\{X_1=1,X_2=0,S=1\}$  est stable et pour E=1, l'état  $\{X_1=0,X_2=0,S=1\}$  est stable.  $\forall E$ , ce circuit est donc **monostable**.

- b) Equation différentielle (ED) : Montrer que  $u_c(t)$  vérifie l'ED :  $\frac{du_c}{dt} + \frac{u_c}{\tau_c} = \frac{n(t)}{\tau_c}$  avec  $\tau_c = RC$ .

- c) Fonctionnement du circuit pour  $T' > RC \cdot \ln 2$ :

- i) On considère une 1<sup>e</sup> phase qui débute à l'instant t=0 tel que E bascule de 1 à 0 et reste dans cet état pendant une durée T'. Pour  $t=0^-$ , le système était dans l'état stable  $\{E=1, X_1=0, X_2=0, S=1\}$  et le condensateur était déchargé.

Montrer qu'à  $t=0^+$ , le système est dans l'état  $\{E=0, X_1=1, X_2=1, \underline{S=0}\}$ .

Tant que le système reste dans cet état, que vaut n(t) ? Résoudre l'ED vérifiée par  $u_c(t)$ . En déduire que  $v(t) = V_{dd} e^{-t/\tau_c}$  et que cette  $\mathbf{1}^e$  phase prend fin à  $t_B = \tau_c$ .  $\ln 2$ .

- ii) Montrer qu'à  $t = t_B^+$ , le système est dans l'état  $\{E = 0, X_1 = 1, X_2 = 0, \underline{S = 1}\}$ . Il s'agit du début de la 2<sup>e</sup> phase pendant laquelle cet état stable perdure, elle se termine a priori à t = T'.

- iii) On considère une  $3^e$  phase qui débute à l'instant t = T' tel que E bascule de 0 à 1 et reste dans cet état pour  $t \in ]T', T[$ .

Montrer qu'à  $t = {T'}^+$ , le système est dans l'état  $\{E = \mathbf{1}, X_1 = \mathbf{0}, X_2 = \mathbf{0}, S = \mathbf{1}\}$ . Cet état stable perdure jusqu'à t = T.

- iv) Tracer le chronogramme de ce système.

- d) Fonctionnement du circuit pour T' < RC.  $\ln 2 = t_B$ : Par un raisonnement analogue,

- i) Justifier que pour  $t \in ]0, T'[, \{E = 0, X_1 = 1, v(t) = V_{dd}e^{-t/\tau_c}, S = 0\}.$

- ii) Justifier que pour  $t \in ]T', t_B[, \{E = 1, X_1 = 1, v(t) = V_{dd}e^{-t/\tau_c}, S = 0\}.$

- iii) Justifier que pour  $t \in ]t_B, T[, \{E = 1, X_1 = 0, X_2 = 0, S = 1\}.$

- e) Montrer que, quel que soit T', la valeur moyenne de s(t) est une fonction affine de la fréquence du signal d'entrée e(t). Commenter.

<u>BILAN</u>: L'état S=0 est un état de durée  $t_B=RC$ . In 2 quel que soit T'. Ce circuit assure donc le rôle de convertisseur fréquence-tension car la valeur moyenne de s(t) est une fonction affine de la fréquence du signal d'entrée e(t).

${\bf NB}$ : Il faut toutefois s'assurer que la **période**  ${\bf T}$  **du signal d'entrée est assez élevée par rapport à \tau\_c** de sorte que  $T>t_B=\tau_c. ln2$  mais aussi pour permettre la décharge complète du condensateur avant le basculement de E de 1 à 0 à T.

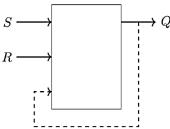

# D) Ex de circuit bistable : bascule RS - mémoire Set-Reset

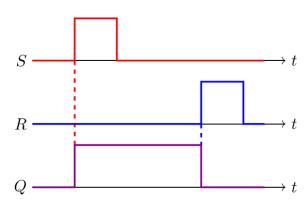

# 1) Comportement d'une bascule RS - Effet mémoire

Une <u>bascule RS</u> a deux entrées principales : **l'entrée «**  $\underline{\text{Set}}$  » notée S et **l'entrée «**  $\underline{\text{Reset}}$  » notée R.

On s'intéresse à une sortie principale du circuit, notée  $\it Q$ .

- lorsque S passe à 1, Q passe à 1 (« set »);

- Q reste à 1 quelle que soit la valeur ultérieure de S (mémoire) ;

- lorsque R passe à 1, la sortie Q passe à 0 (« reset »);

- Q reste à 0 quelle que soit la valeur ultérieure de R (mémoire).

### Chronogramme:

**NB**: Le cas S = R = 1 n'est pas possible dans les utilisations normales de la bascule RS.

Le chronogramme montre que, pour S=R=0, la sortie Q peut prendre la valeur 0 ou 1 selon « l'histoire » du circuit : ce comportement est celui d'un système séquentiel. C'est ce qui constitue « <u>l'effet</u> mémoire ».

L'équation donnant la sortie d'une bascule RS est donc donnée par une relation combinatoire de la forme :

$$Q_+ = f(S, R, Q_-)$$

où  $Q_{-/+}$  est la valeur de la sortie avant/après la modification d'une entrée.

$\underline{Rq}$  : on note parfois  $Q_n$  à la place de  $Q_-$  et  $Q_{n+1}$  à la place de  $Q_+$ .

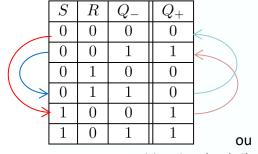

| S | R | $Q_{n+1}$ |

|---|---|-----------|

| 0 | 0 | $Q_n$     |

| 1 | 0 | 1         |

| 0 | 1 | 0         |

Tables de vérité d'une bascule RS

(rappel : le cas S = R = 1 n'est pas possible dans les utilisations normales de la bascule RS)

La bascule RS est un système <u>bistable</u>: en effet, pour le jeu de données d'entrée R=S=0, les états Q=0 et Q=1 sont stables  $(Q_+=Q_-)$ .

« **Set** » (inscription ou initialisation) : On passe de l'état  $\{S = R = 0, Q = 0\}$  à l'état  $\{S = R = 0, Q = 1\}$  par une **impulsion de** S i.e. S bascule de S i.e. S i.e. S bascule de S

« Reset » (effacement ou réinitialisation) : On passe de l'état  $\{S=R=0,Q=1\}$  à l'état  $\{S=R=0,Q=0\}$  par une **impulsion de** R i.e. R bascule de 0 à 1 puis rebascule à 0.

# 2) Réalisations pratiques (Cours-TD)

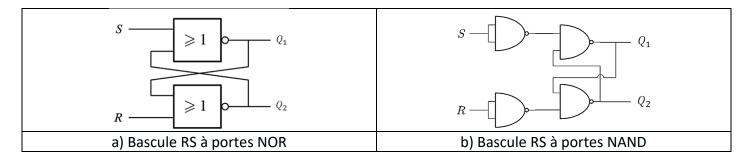

Puisque la table de vérité ne précise pas l'état de sortie pour S=R=1, plusieurs circuits logiques correspondent à une bascule RS.

## **⊃** Etude du circuit a) :

Pour ce circuit, on identifie deux entrées principales S et R et deux sorties principales  $Q_1$  et  $Q_2$ .

i) Relation combinatoire : dans la suite, on note  $\mathcal{Q}_2 = \mathcal{Q}$

Montrer que la sortie Q est donnée par la relation :

$$Q_+ = \bar{R} \cdot (S + Q_-)$$

Construire la table de vérité correspondant à cette relation. Identifier les états stables.

Vérifier que ce circuit correspond à une bascule RS.

Montrer que, dans les cas acceptés d'utilisation de la bascule RS,  $Q_1=\overline{Q}$ .

### ii) Mémoire à effacement prioritaire

Vérifier que, pour S = R = 1, on a  $Q_+ = 0$ .

On parle donc de mémoire à effacement prioritaire :  $\forall S, R = 1 \Longrightarrow Q_+ = 0$ .

#### **⊃** Etude du circuit b) :

Pour ce circuit, on identifie deux entrées principales S et R et deux sorties principales  $Q_1$  et  $Q_2$ .

i) Relation combinatoire : dans la suite, on note  $Q_1 = Q$

Montrer que la sortie Q est donnée par la relation :

$$Q_+ = S + (\bar{R} \cdot Q_-)$$

Construire la table de vérité correspondant à cette relation. Identifier les états stables.

Vérifier que ce circuit correspond à une bascule RS.

Comme pour le circuit a), on peut montrer que, dans les cas acceptés d'utilisation de la bascule RS,  $Q_2 = \overline{Q}$ .

## ii) Mémoire à inscription prioritaire

Vérifier que, pour S = R = 1, on a  $Q_+ = 1$ .

On parle donc de mémoire à inscription prioritaire :  $\forall R, S = 1 \Longrightarrow Q_+ = 1$ .