# TDE4 – Logique séquentielle

| Capacités exigibles                                                                                 | ChE4 | Ex1 | Ex2 | Ex3 | Ex4 | TP5 |

|-----------------------------------------------------------------------------------------------------|------|-----|-----|-----|-----|-----|

| États stables.                                                                                      |      |     |     |     |     |     |

| Circuits astable, monostable, bistable.                                                             |      |     |     |     |     |     |

| Déterminer les états stables d'un circuit contenant des portes logiques, avec rétroaction.          | •    |     | •   |     |     | •   |

| Réaliser un oscillateur à l'aide d'un circuit astable à portes logiques.                            |      |     |     |     |     |     |

| Réaliser un convertisseur fréquence tension utilisant un circuit monostable à porte logique.        |      |     |     |     |     |     |

| Bascule RS à portes NAND ou NOR.                                                                    |      |     |     |     |     |     |

| Décrire le fonctionnement d'une bascule RS dont le schéma est fourni.                               | •    | •   | •   | •   | •   | •   |

| Expliquer comment réaliser une mémoire à l'aide d'un circuit bistable.                              |      |     |     |     |     |     |

| Chronogramme.                                                                                       |      |     |     |     |     |     |

| Déterminer le chronogramme des grandeurs électriques pertinentes d'un circuit comportant des portes | •    | •   | •   | •   |     |     |

| logiques.                                                                                           |      |     |     |     |     |     |

## 0 Exercices classiques vus en cours :

**B.1 et 2**: Etude de circuits astables

**C** : Etude d'un circuit monostable : convertisseur fréquence-tension

D.2: Etude de circuits bistables: bascule RS

#### 1 Chronogrammes d'une bascule RS

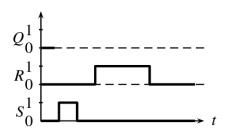

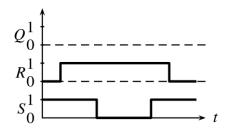

Compléter les chronogrammes suivants relatifs à une bascule RS à effacement prioritaire.

1.

2.

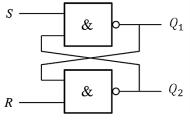

### 2 / Bascule à deux portes NAND

- 1. Établir la table de vérité de la bascule RS à portes NAND représentée ci-dessus et proposer un chronogramme mettant en évidence les « phases » d'inscription (set), d'effacement (reset) et de mémorisation.

- 2. Comment modifier ce circuit, en rajoutant uniquement d'autres portes NAND, pour obtenir la même table de vérité que celle de la bascule RS vue dans le cours ?

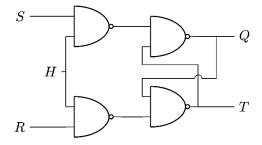

#### 3 / Système à mémoire RSH

La bascule RS (bascule « asynchrone ») présentée dans le cours a un inconvénient majeur : elle peut enregistrer un signal parasite sur l'entrée R ou S, faisant évoluer la bascule alors qu'il n'y avait pas lieu d'être. Pour éviter ce problème, il suffit de ne prendre en compte les valeurs présentes sur les entrées R et S que pendant un temps très court. On réalise ceci grâce au signal supplémentaire H (signal d'Horloge) sur lequel on enverra l'impulsion permettant la prise en compte des entrées.

On étudie donc un système séquentiel à trois entrées principales H, S et R dont la sortie est notée Q. Le fonctionnement est le suivant :

- $\triangleright$  tant que H=1, le système est une mémoire RS;

- $\triangleright$  si H=0, le système est isolé, son état mémoire est constant.

L'équation combinatoire du système dépend de quatre variables et vaut

$$Q_{+} = H \cdot (S \cdot \bar{Q}_{-} + \bar{R} \cdot Q_{-}) + \bar{H} \cdot Q_{-}.$$

- 1. Tracer le chronogramme représentant des évolutions de R, S, H et Q en fonction du temps.

- 2. Montrer que cette relation combinatoire correspond bien au cahier des charges décrit dans l'énoncé.

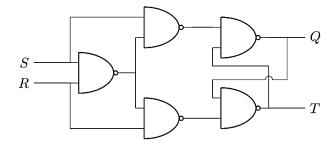

On considère le circuit logique suivant.

- 3. Vérifier que ce montage vérifie la relation combinatoire proposée.

- 4. Montrer que  $T = \bar{Q}$  dans les cas d'utilisation acceptés de la bascule RS.

Rq: l'entrée H est parfois notée C, pour Clock.

#### 4 Bascule RS à cinq portes NAND

On étudie un système séquentiel à deux entrées principales S et R dont la sortie est notée Q. L'équation combinatoire du système est :

$$Q_+ = S \cdot \bar{R} + (S + \bar{R}) \cdot Q_- .$$

- 1. Montrer que cette relation combinatoire est celle d'une mémoire Set-Reset.

- 2. Quel est l'effet de ce système si R = S = 1?

On considère le circuit logique suivant.

- 3. Vérifier que ce montage vérifie la relation combinatoire proposée.

- 4. Montrer que  $T = \bar{Q}$  dans les cas acceptés d'utilisation de la bascule RS.