# Préparation aux oraux MPI TD1' – Electronique logique

### **Rapports**

#### CCINP 2023/2024

Dans le cas particulier de la filière MPI, les exercices comportant des portes logiques sont plutôt bien réussis dans l'ensemble.

## 1 Exercice « académique » : Porte universelle

On s'intéresse à la porte logique NOR qui est une porte universelle.

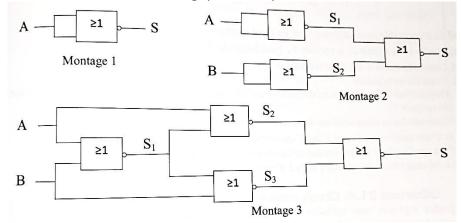

1) Etablir la table de vérité et la fonction logique correspondant à chacun des montages suivants :

- 2) Proposer un montage réalisant une porte XOR (ou-exclusif) uniquement à partir de portes NOR.

- 3) Etablir un script python permettant de vérifier la validité du montage.

#### Données :

Le programme :

```

s_not=[(a,not a) for a in [False,True]]

print("Table NOT :",s_not)

renvoie:

```

Table NOT : [(False, True), (True, False)]

Le programme :

```

s_or=[((a,b),a or b) for a in [False,True] for b in [False,True]]

print("Table OR :",s_or)

```

renvoie:

Table OR: [((False, False), False), ((False, True), True), ((True, False), True), ((True, True), True)]

# 2 Exercice « académique » : Réalisation d'une bascule RS à inscription prioritaire à l'aide de portes élémentaires non universelles

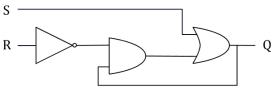

Justifier que le montage ci-dessous réalise l'opération logique associée à une bascule RS à inscription prioritaire.

# 3 Exercice « académique » : Convertisseur fréquence-tension [monostable]

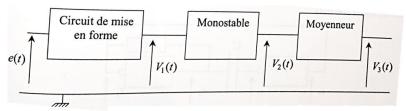

On réalise un convertisseur fréquence-tension à l'aide du montage ci-dessous constitué de l'enchaînement de trois blocs :

L'objectif est d'obtenir en sortie du moyenneur une tension  $V_3$  continue proportionnelle à la fréquence  $f_0$  de la tension d'entrée alternative  $e(t) = Asin(2\pi f_0 t)$ .

Le 1<sup>er</sup> bloc est un circuit de mise en forme comportant notamment un amplificateur linéaire intégré suivi d'un conducteur ohmique et d'une diode. Il agit comme un comparateur simple :

$$\begin{cases} V_1(t) = +15 \text{V (niveau haut)} & \text{si } e(t) > E_0 \\ V_1(t) = 0 \text{V (niveau bas)} & \text{si } e(t) < E_0 \end{cases}$$

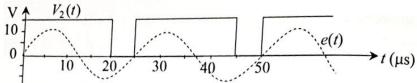

1) Représenter le chronogramme e(t) et  $V_1(t)$  dans le cas où l'on choisit  $E_0=0$ . Le 2<sup>e</sup> bloc correspond à un circuit logique monostable. Les signaux e(t) (en pointillés) et  $V_2(t)$  (en trait continu) sont représentés ci-après :

- 2) Définir ce qu'est un circuit monostable et indiquer si ce circuit est déclenché par un front montant ou descendant de  $V_1(t)$ .

- 3) Que vaut  $V_2$  dans l'état instable ?

- 4) Mesurer la durée  $\tau$  de l'état instable.

Le 3<sup>e</sup> bloc est un filtre moyenneur.

- 5) Proposer un circuit permettant de réaliser un moyenneur. Comment choisir sa fréquence de coupure ?

- 6) Cette condition étant vérifiée, donner la valeur de  $V_3$  en fonction de  $\tau$ ,  $f_0$  et d'une tension E que l'on définira.

- 7) Pour quelle plage de fréquences de la tension e(t) ce montage est-il adapté ?

- 8) Le montage testé sur un signal d'entrée e(t) de fréquence adaptée donne  $V_3=3\,V$ . Quelle est la fréquence de e(t) ?

# 4 Résolution de problème : Oscillateur à portes logiques

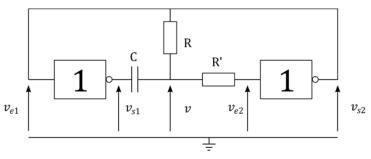

On considère le circuit ci-contre :

On note  $V_{DD}$  la tension d'alimentation des portes logiques qui correspond à la valeur du niveau haut des signaux de sortie des portes. On note  $V_b$  la tension seuil des portes.

1) Montrer que ce circuit est astable.

On suppose à t<0 que  $v_{s2}=v_{e1}=V_{DD}$  ; cette phase s'achève lorsque  $v_{e2}=V_b$  et cet instant est choisi comme origine des temps.

2) Déterminer la période des différents signaux générés par ce circuit. Simplifier son expression dans le cas où  $V_b=\frac{V_{DD}}{2}$ .