# TP5 - Electronique logique

Compétences expérimentales au programme :

| Électronique logique.             | Mettre en œuvre divers montages utilisant des portes logiques.              |

|-----------------------------------|-----------------------------------------------------------------------------|

| Logique séquentielle et stabilité | Réaliser un oscillateur à l'aide d'un circuit astable à portes logiques.    |

|                                   | Réaliser un convertisseur fréquence tension utilisant un circuit monostable |

|                                   | à porte logique.                                                            |

#### Objectifs:

- § A : Réaliser un montage permettant de valider la table de vérité de portes logiques. Identifier la tension seuil d'une porte logique.

- § B : Réaliser et étudier expérimentalement un oscillateur à l'aide d'un circuit astable à portes logiques. Estimer l'ordre de grandeur du temps de commutation d'une porte logique.

- § C : Réaliser et étudier expérimentalement un convertisseur fréquence-tension utilisant un circuit monostable à porte logique.

- § D : Réaliser une bascule RS à l'aide d'un circuit bistable à portes NAND.

# A faire pour le jeudi 13/11 : Lire et répondre aux questions ✔.

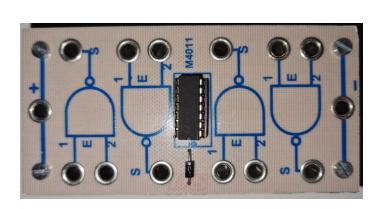

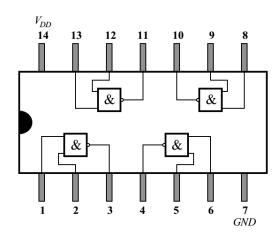

Nous allons étudier des circuits à portes logiques, en utilisant le composant CMOS 4011 qui supporte l'équivalent de 4 portes NAND et dont un extrait de la fiche technique est donné au DOC 1.

On alimente ce composant par une tension continue entre les bornes  $V_{DD}$  et GND (ground = masse) délivrée par l'alimentation stabilisée Jeulin EVO2. Sauf mention contraire, on choisira cette tension égale à 10 V.

# A) Validation expérimentale de tables de vérité

<u>Objectifs</u> : Réaliser un montage permettant de valider la table de vérité de portes logiques. Identifier la tension seuil d'une porte logique.

#### 1) Porte NOT

- ✓ 1. A l'aide d'un schéma préciser comment réaliser une porte NOT à l'aide du composant CMOS 4011 ?

Note Après validation, réaliser le montage avec une tension d'alimentation entre les bornes  $V_{DD}$  et GND égale à 10 V. On utilise le GBF en mode DC pour générer la tension d'entrée de la porte et le voltmètre pour mesurer la tension de sortie.

- $oldsymbol{\circ}$  2. Faire varier la tension d'entrée  $u_E$  (dans un intervalle judicieusement choisi) et relever les valeurs de tension de sortie pour valider la table de vérité de la porte NOT. Identifier les tensions seuil de commutation haute et basse  $V_{sb}$  et  $V_{sh}$ :

$u_E < V_{sb}$  correspond à E=0 et  $u_E > V_{sh}$  correspond à E=1

Justifier que l'approximation  $V_{sh} \approx V_{sh}$ , utilisée en théorie, est légitime.

Mener à nouveau l'étude avec une tension d'alimentation entre les bornes  $V_{DD}$  et GND égale à 5 V.

$oldsymbol{\supseteq}$  3. Justifier que l'approximation  $V_{\scriptscriptstyle S} pprox rac{V_{DD}}{2}$ , utilisée en théorie, est légitime.

#### 2) Porte NAND

- Avec une tension d'alimentation entre les bornes  $V_{DD}$  et GND égale à 10 V, réaliser différentes combinaisons de tensions d'entrée  $(u_A, u_B)$  pour valider la table de vérité de la porte NAND. Pour tester le cas des signaux logiques (A=1, B=1), on utilisera pour une entrée la tension du GBF en mode DC et pour l'autre entrée la tension de l'alimentation stabilisée.

- → 4. Relever les valeurs de tension de sortie. Commenter.

# B) Oscillateurs à portes logiques

<u>Objectifs</u> : Réaliser et étudier expérimentalement un oscillateur à l'aide d'un circuit astable à portes logiques. Estimer l'ordre de grandeur du temps de commutation d'une porte logique.

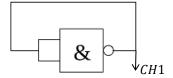

### 1) Oscillateur à une porte NOT

$^ ext{#V}$  Réaliser le circuit suivant avec une tension d'alimentation entre les bornes  $V_{DD}$  et GND égale à 10 V :

- ⇒ 6. Vérifier que le signal mesuré à l'oscilloscope est périodique et mesurer sa période d'oscillation.

Mener à nouveau l'étude avec une tension d'alimentation entre les bornes  $V_{DD}$  et GND égale à 5 V.

⇒ 7. Commenter en vous appuyant sur la fiche technique.

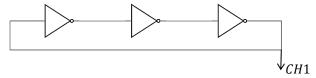

#### 2) Oscillateur à trois portes NOT

On a étudié théoriquement au Ch.E4 le circuit ci-dessous.

$^{ t t}$  Réaliser le circuit suivant avec une tension d'alimentation entre les bornes  $V_{DD}$  et GND égale à 10 V :

■ 8. Vérifier que le signal mesuré à l'oscilloscope est périodique et mesurer sa période d'oscillation. Commenter en comparant à la période mesurée pour l'oscillateur à 1 porte NOT.

# C) Convertisseur fréquence-tension

<u>Objectif</u>: Réaliser et étudier expérimentalement un convertisseur fréquence-tension utilisant un circuit monostable à porte logique.

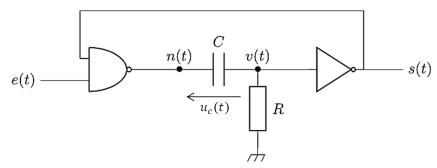

On a étudié théoriquement au Ch.E4 le circuit ci-dessous :

- $\bigcirc$  9. Vérifier que l'hypothèse « temps de commutation  $\tau$  des portes logiques très inférieur au temps caractéristique du circuit  $\tau_c = RC$  », utilisée en théorie, est légitime.

- $^{\heartsuit}$  Réaliser le circuit avec une tension d'alimentation entre les bornes  $V_{DD}$  et GND égale à 10 V, on prendra  $C = 10 \ nF$  et  $R = 10 \ k\Omega$ .

- lacktriangle 10. Imposer une tension  $u_E$  constante quelconque en entrée du circuit et vérifier que la sortie est toujours dans l'état S=1. Commenter en comparant aux résultats théoriques.

- $oldsymbol{\supset}$  11. Imposer une tension  $u_E$  créneau oscillant entre 0 et  $V_{DD}$  de fréquence  $f=500\,Hz$  en entrée du circuit. Vérifier que le signal mesuré à l'oscilloscope est un créneau. Comparer aux résultats théoriques en mesurant  $t_B$  la durée de l'état S=0.

- $\supset$  12. Modifier successivement la fréquence et le rapport cyclique du créneau (« duty cycle ») et vérifier que la durée  $t_B$  de l'état S=0 est indépendante de ces deux paramètres.

On veut vérifier expérimentalement que le circuit assure le rôle de convertisseur fréquence-tension.

- 13. D'après l'étude théorique, pour quelle fréquence maximale le circuit assure-t-il ce rôle?

- № 3 14. Proposer un protocole, en précisant le matériel utilisé, permettant de vérifier que le circuit est un convertisseur fréquence-tension.

- Après validation, mettre en œuvre ce protocole.

- ⇒ 15. Analyser les résultats obtenus.

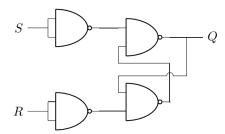

# D) Bascule RS à inscription prioritaire (paillasse prof)

Objectif: Réaliser une bascule RS à l'aide d'un circuit bistable à portes NAND.

On rappelle qu'une bascule RS à inscription prioritaire peut être réalisée avec le circuit à portes NAND suivant :

On réalise le circuit avec une tension d'alimentation entre les bornes  $V_{DD}$  et GND égale à 10 V.

⇒ 16. Vérifions expérimentalement que ce montage a le comportement d'une bascule RS :

- Partons de l'état (S,R) = (0,0), préciser la sortie Q, lorsque l'entrée S passe de l'état 0 à l'état 1 (l'entrée R restant égale à 0);

- Pour R=0, préciser la sortie Q, lorsque l'entrée S change d'état (pour cela, on fait varier  $u_S$  de  $V_{DD}$  à 0 puis de 0 à  $V_{DD}$ ) ;

- Partons de l'état (S,R) = (0,0), préciser la sortie Q, lorsque l'entrée R passe de l'état 0 à l'état 1 (l'entrée S restant égale à 0);

- Pour S=0, préciser la sortie Q, lorsque l'entrée R change d'état (pour cela, on fait varier  $u_R$  de  $V_{DD}$  à 0 puis de 0 à  $V_{DD}$ ).

# DOC 1 : Extraits de la fiche technique du CMOS 4011 utilisé

## DC Electrical Characteristics CD4001BC, CD4011BC (Note 2)

| Symbol          | Parameter                                | Conditions                                                                                                                                                    | −40°C                 |                      | +25°C                 |                         |                      | + 85°C                |                      | Units          |

|-----------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|----------------------|-----------------------|-------------------------|----------------------|-----------------------|----------------------|----------------|

|                 |                                          |                                                                                                                                                               | Min                   | Max                  | Min                   | Тур                     | Max                  | Min                   | Max                  | Oilits         |

| I <sub>DD</sub> | Quiescent Device<br>Current              | $V_{DD} = 5V, V_{IN} = V_{DD} \text{ or } V_{SS}$<br>$V_{DD} = 10V, V_{IN} = V_{DD} \text{ or } V_{SS}$<br>$V_{DD} = 15V, V_{IN} = V_{DD} \text{ or } V_{SS}$ |                       | 1<br>2<br>4          |                       | 0.004<br>0.005<br>0.006 | 1<br>2<br>4          |                       | 7.5<br>15<br>30      | μΑ<br>μΑ<br>μΑ |

| V <sub>OL</sub> | Low Level<br>Output Voltage              | $ \begin{vmatrix} V_{DD} = 5V \\ V_{DD} = 10V \\ V_{DD} = 15V \\ \end{vmatrix}  I_O  < 1 \ \mu A $                                                            |                       | 0.05<br>0.05<br>0.05 |                       | 0 0 0                   | 0.05<br>0.05<br>0.05 |                       | 0.05<br>0.05<br>0.05 | V<br>V         |

| V <sub>OH</sub> | High Level<br>Output Voltage             | $ \begin{vmatrix} V_{DD} = 5V \\ V_{DD} = 10V \\ V_{DD} = 15V \\ \end{vmatrix}  I_O  < 1 \ \mu A $                                                            | 4.95<br>9.95<br>14.95 |                      | 4.95<br>9.95<br>14.95 | 5<br>10<br>15           |                      | 4.95<br>9.95<br>14.95 |                      | V<br>V         |

| V <sub>IL</sub> | Low Level<br>Input Voltage               | $V_{DD} = 5V, V_{O} = 4.5V$<br>$V_{DD} = 10V, V_{O} = 9.0V$<br>$V_{DD} = 15V, V_{O} = 13.5V$                                                                  |                       | 1.5<br>3.0<br>4.0    |                       | 2<br>4<br>6             | 1.5<br>3.0<br>4.0    |                       | 1.5<br>3.0<br>4.0    | V<br>V         |

| V <sub>IH</sub> | High Level<br>Input Voltage              | $V_{DD} = 5V, V_{O} = 0.5V$<br>$V_{DD} = 10V, V_{O} = 1.0V$<br>$V_{DD} = 15V, V_{O} = 1.5V$                                                                   | 3.5<br>7.0<br>11.0    |                      | 3.5<br>7.0<br>11.0    | 3 6 9                   |                      | 3.5<br>7.0<br>11.0    |                      | V<br>V         |

| l <sub>OL</sub> | Low Level Output<br>Current<br>(Note 3)  | $V_{DD} = 5V, V_{O} = 0.4V$<br>$V_{DD} = 10V, V_{O} = 0.5V$<br>$V_{DD} = 15V, V_{O} = 1.5V$                                                                   | 0.52<br>1.3<br>3.6    |                      | 0.44<br>1.1<br>3.0    | 0.88<br>2.25<br>8.8     |                      | 0.36<br>0.9<br>2.4    |                      | mA<br>mA<br>mA |

| I <sub>OH</sub> | High Level Output<br>Current<br>(Note 3) | $V_{DD} = 5V, V_{O} = 4.6V$<br>$V_{DD} = 10V, V_{O} = 9.5V$<br>$V_{DD} = 15V, V_{O} = 13.5V$                                                                  | -0.52<br>-1.3<br>-3.6 |                      | -0.44<br>-1.1<br>-3.0 | -0.88<br>-2.25<br>-8.8  |                      | -0.36<br>-0.9<br>-2.4 |                      | mA<br>mA<br>mA |

| I <sub>IN</sub> | Input Current                            | $V_{DD} = 15V, V_{IN} = 0V$<br>$V_{DD} = 15V, V_{IN} = 15V$                                                                                                   |                       | -0.30<br>0.30        |                       | -10 <sup>-5</sup>       | -0.30<br>0.30        |                       | -1.0<br>1.0          | μA<br>μA       |

$\begin{array}{ll} \textbf{AC Electrical Characteristics}^* \text{ } \text{CD4011BC, CD4011BM} \\ \text{T}_A = 25^{\circ}\text{C, Input } t_r; t_f = 20 \text{ ns. C}_L = 50 \text{ pF, R}_L = 200 \text{k. Typical Temperature Coefficient is } 0.3\%/^{\circ}\text{C.} \end{array}$

| Symbol                              | Parameter                  | Conditions     | Тур | Max | Units |  |

|-------------------------------------|----------------------------|----------------|-----|-----|-------|--|

| t <sub>PHL</sub>                    | Propagation Delay,         | $V_{DD} = 5V$  | 120 | 250 | ns    |  |

|                                     | High-to-Low Level          | $V_{DD} = 10V$ | 50  | 100 | ns    |  |

|                                     |                            | $V_{DD} = 15V$ | 35  | 70  | ns    |  |

| t <sub>PLH</sub>                    | Propagation Delay,         | $V_{DD} = 5V$  | 85  | 250 | ns    |  |

|                                     | Low-to-High Level          | $V_{DD} = 10V$ | 40  | 100 | ns    |  |

|                                     |                            | $V_{DD} = 15V$ | 30  | 70  | ns    |  |

| t <sub>THL</sub> , t <sub>TLH</sub> | Transition Time            | $V_{DD} = 5V$  | 90  | 200 | ns    |  |

|                                     |                            | $V_{DD} = 10V$ | 50  | 100 | ns    |  |

|                                     |                            | $V_{DD} = 15V$ | 40  | 80  | ns    |  |

| C <sub>IN</sub>                     | Average Input Capacitance  | Any Input      | 5   | 7.5 | pF    |  |

| C <sub>PD</sub>                     | Power Dissipation Capacity | Any Gate       | 14  |     | pF    |  |

<sup>\*</sup>AC Parameters are guaranteed by DC correlated testing.