# ELEC3 - Électronique à portes logiques

Travaux dirigés

#### Exercice 1: Universalité de la porte NAND \*

On peut montrer qu'il est possible de créer n'importe quelle fonction logique par combinaison de portes NAND exclusivement.

- 1. Expliquer comment créer une porte NOT à partir d'une porte NAND.

- 2. Comment créer une porte AND à partir de deux portes NAND?

#### Exercice 2: Simplifications de montages $\star$

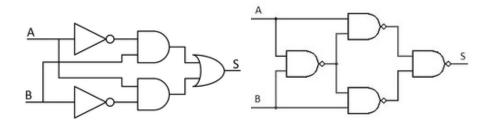

On considère les deux circuits suivants :

- 1. Établir la table de vérité de chacun de ces circuits.

- 2. Montrer que ces montage peut être simplifié en une seule porte logique en la précisant dans chaque cas.

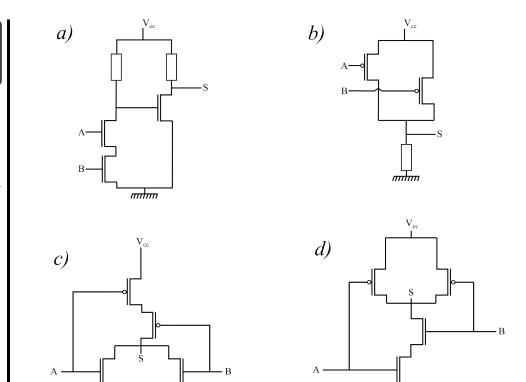

# Exercice 3: Portes réalisées à l'aide d'interrupteurs commandés $\star$

1. Pour chacun des montages suivants, préciser la fonction de la porte réalisée en établissant la table de vérité.

2. Quel est l'intérêt des portes c et d par rapport aux portes a et b?

#### Exercice 4: Chiffrement symétrique à fonction XOR \*\*

Un moyen de chiffrer un message constitué d'une suite de N bits  $e_i$ , pour i de 1 à N est d'utiliser une suite de bits  $c_i$ , pour i de 1 à N, fabriquée par un générateur pseudoaléatoire. Le message chiffré qu'envoie l'expéditeur au destinataire est la suite définie par  $s_i = (e_i \text{ XOR } c_i)$  pour i de 1 à N.

- 1. Rappeler la table de vérité de la porte XOR, et justifier que le message est chiffré.

- 2. Montrer que le destinataire, connaissant la suite de bits  $c_i$ , qui est la clé de chiffrement, retrouve le message d'origine en calculant  $(s_i \text{ XOR } c_i)$  pour i de 1 à N.

### Exercice 5: Un circuit séquentiel simple \*\*

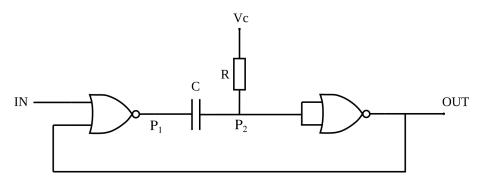

On considère le circuit suivant :

P. BERTIN

Les deux portes sont supposées appeler un courant nul à leurs entrées, et un niveau logique est interprété comme haut dès lors que le potentiel est supérieur à  $V_c/2$ . Pour les applications numérique, on prendra  $C=0.1\,\mu\mathrm{F}$  et  $R=10\,\mathrm{k}\Omega$ .

Le circuit étant tel que IN=0 depuis longtemps (état A), on impose une courte impulsion à IN, qui passe très brièvement à 1 avant de revenir à 0 (état B)

- 1. Donner les valeurs des potentiels aux point  $P_1$ ,  $P_2$  et OUT pour les états A et B.

- 2. Justifier le fait que R et C peuvent être considérés en série. En déduire l'expression de  $V(P_2) = f(t)$ .

- 3. En déduire littéralement et numériquement le temps nécessaire  $t_B$  pour que OUT change d'état à nouveau.

- 4. Quelle est la nature de ce circuit logique?

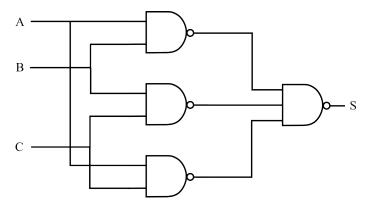

#### Exercice 6: Porte logique majoritaire 3 entrées \*\*

Le circuit ci-dessous est nommé circuit logique majoritaire. Établir sa table de vérité et justifier son nom.

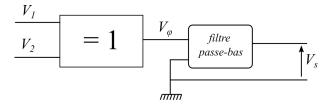

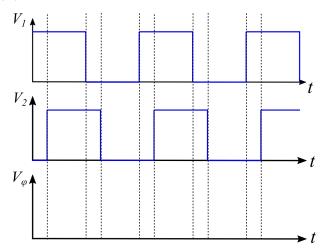

Exercice 7: Comparateur de phase \*

Un comparateur de phase a pour but de délivrer un signal proportionnel à la différence de phase entre deux signaux.

$$V_s = K |\varphi_1 - \varphi_2| \text{ avec } K = \frac{V_0}{\pi}$$

Il peut être réalisé par une porte logique XOR suivi d'un filtre passe-bas. Les signaux d'entrée sont des signaux numériques, représentés par les niveaux 0 et 1. La période des signaux d'entrée est de  $T=10\,\mathrm{kHz}$ .

1. Compléter le chronogramme ci-dessous et expliquer simplement le principe de fonctionnement.

- 2. Préciser comment doit être choisis le filtre passe-bas utilisé, et proposer un montage simple permettant de le réaliser en précisant les valeurs des composants choisis.

- 3. Préciser quelques valeurs de  $V_S$  pour quelques valeurs remarquables de  $\Delta \varphi$ . Ce comparateur permet-il de mesurer le signe du déphasage?

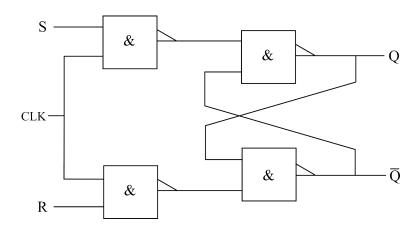

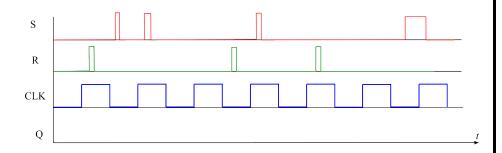

### Exercice 8: Circuit séquentiel avec horloge \*\*

Pour éviter les erreurs de lecture ou d'écriture, les mémoires utilisent un signal d'horloge (souvent désigné par CLK, pour *clock*). On se propose de faire apparaître l'intérêt sur le circuit suivant :

P. BERTIN

- 1. Que reconnaît-on dans la partie droite de ce montage? Expliquer le fonctionnement de cette partie.

- 2. Compléter le chronogramme suivant pour le montage suivant en admettant qu'à t=0, on a Q=0.

**3**. En vous appuyant sur le chronogramme précédent, expliquer à quoi peut servir le signal d'horloge dans le cadre de l'utilisation d'une mémoire.

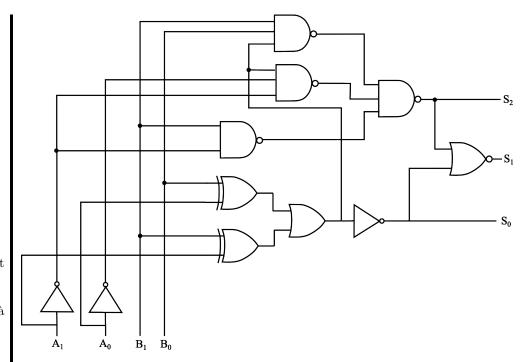

## Exercice 9: Le défi combinatoire \*\*\*

Ce circuit à portes logiques paraît bien mystérieux... les entrées  $A_0$  et  $A_1$  représentent un nombre codé sur 2 bits. Par exemple,  $A_0 = 0$ ,  $A_1 = 1$  représente le binaire A = 10, soit 2 en décimal (idem pour B). Déterminer la fonction de ce montage.

P. BERTIN